- Discovery MR750w and SIGNA™ Architect T 3.0T System Service Methods

- 5690002-2EN Revision 4

- 00000018WIA30B5A460GYZ

- id_20317971.12

- Jul 13, 2021 4:05:20 PM

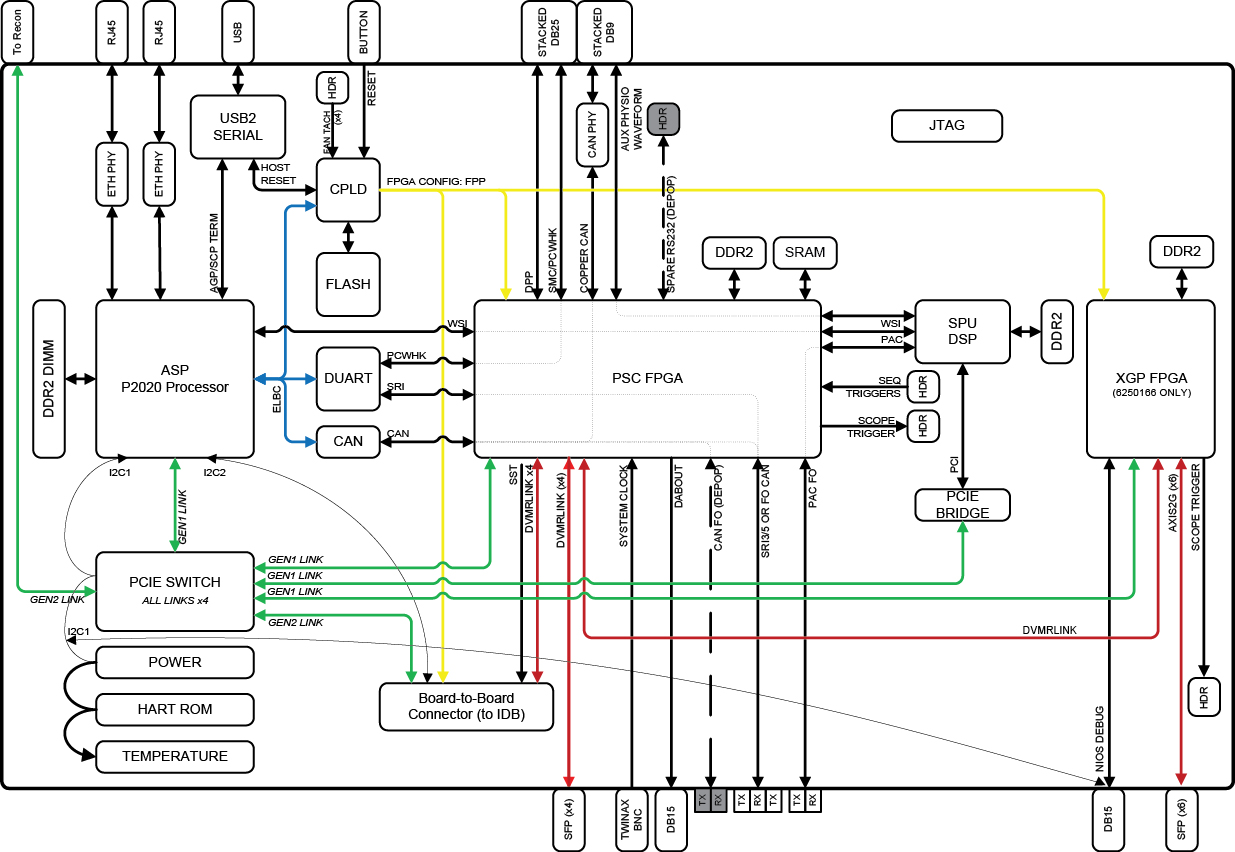

ICE internal board

ICE Mother Board (IMB)

The IMB is one of two boards that may exist in the ICE High Level Assembly (HLA). The IMB contains all of the base SSC functions and can operate with or without a daughter board in a system that requires 32 (or fewer) receive channels and up to two parallel transmit channels. The ICE Daughter Board (IDB) allows expansion of this system up to 160 receive channels and eight parallel transmit channels.

IMB features:

- P2020 Dual Core PowerPC with real-time VxWorks OS.

- High-speed PCIe replaced cPCI backplane.

- USB-to-serial on board for host communication.

- Sequencer, DVMRlink comm., VRF in one PSC FPGA

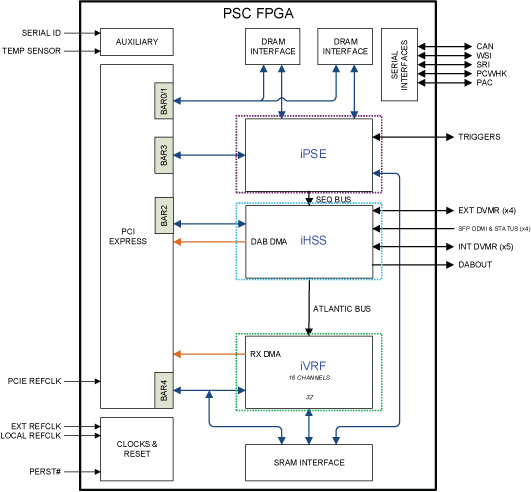

PSC FPGA

- iPSE

- Sequence processor: Accesses DDR2 SDRAM to construct SSP/RF/Grad waveform data.

- WARP: Applies rotation matrix for oblique scan, eddy current compensation for B0, B0 drift compensation.

- SEU (sync exec unit): Synchronize sequence data playout on sequence bus with trigger and 4us tick.

- iHSS

- Interfaces with four external and five internal DVMRlinks.

- (For DPP receive chain systems) Delay module exists to establish synchronized DVMRlink communication from the IMB and IDB.

- FDM as new function for data validity check which replaces monitor fifo in iPSE.

- iVRF

- Decimation filter for received data from the receive chain.

- R2 digital gain adjustment.

- Two 16 channel-supported modules.

- Filtered data DMA transfer to recon via PCIe.