- Topic ID: id_11038801

- Version: 3.0

- Date: Mar 28, 2022 9:32:16 AM

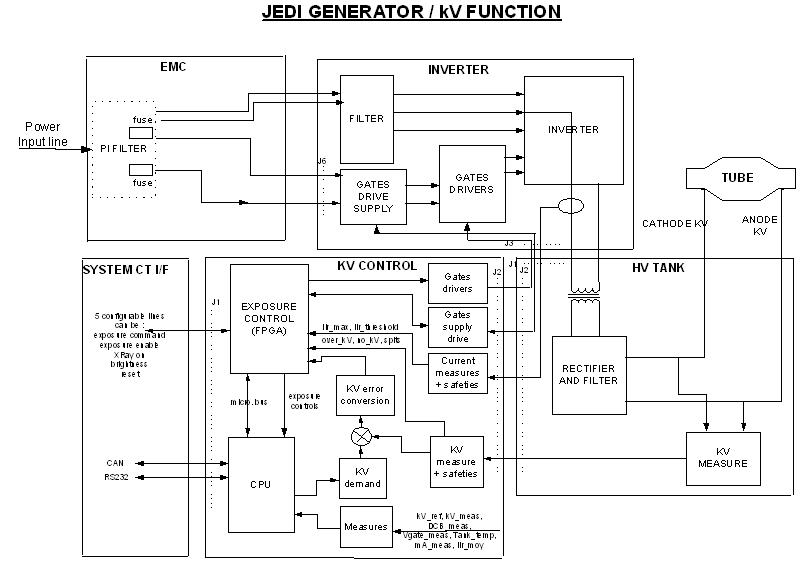

kV Control

kV control function is the main control of the generator.

Figure 1.

1 Introduction

Its main functions are the following:

-

CPU which runs the generator software:

-

Console and/or system communication

-

Exposure sequencing (rotation, heater, exposure control)

-

mA regulation

-

Tube and generator thermal protection

-

Generator configuration management

-

Filament aging

-

Generator diagnostics (application background diagnostics and service diagnostics)

-

-

Standard interface to system interface

-

Control bus interface

-

Exposure control

-

HV power inverter control

-

IGBT gate drive supply control

-

HV chain measures and safeties (kV, mA, inverter currents, inverter gate supply, DC bus)

2 CPU core

CPU is a Power PC micro controller based CPU running at 50MHz.

Program memory is a 2Mbytes flash memory, which allows the software to be downloaded through the system or laptop communication path.

Data memory contains a 256Kbytes RAM and 32Kbytes battery backed-up RAM used to store the configuration/calibration/error log data. This memory also includes a clock used mainly for thermal algorithm calculation.

The generator software is based on VxWorks operating system and divided into several tasks and layers:

-

Communication tasks controls the various communication paths provided by the CPU

-

Application task handles the exposure state machine

-

Thermal management task

-

Device controller tasks which identifies and then drives the kV control, mA control, heater and rotation functions

Calibration and diagnostic functions are also part of the generator software

3 Standard interface to system interface

kV control provides a standard interface on which various system interfaces can be plugged depending on the system configuration.

This “standard” interface provides:

-

a CAN communication line

-

5 UART lines

-

5 configurable IO lines

-

4 system interface identifier lines

4 Control bus

kV control is connected to the generator internal communication bus :

-

CAN communication line used to drive heater and rotation functions

-

mains_drop ( from LVPS board to signal without delay a drop on the main supply )

-

speed_cons_to_rotor (spare)

-

+15V (used to create locally 5V supply)

-

-15V

CAN is a network developed and standardized by the car industry.

Its main purpose is to bring short command messages in hostile environments over few meters up to hundreds of meters with a guaranteed latency and without any information loss.

Defined for small systems, it does not require large amounts of software to encode and decode the messages.

The network hardware is based on a differential line (2 wires) driven at each node by a CAN driver (ISO/DIS 11898 standard).

The length of the network defines the maximum network speed: 1Mbit/s max up to 30m length, 500Kb/s up to 100m.

The messages have a fixed length. Their structure is the following:

-

An identifier field which defines at the same time the command number and the priority of the command (smaller the command number is, higher is the priority)

-

8 bytes of data max

-

Checksum of the message

The CAN protocol ensures that:

-

The highest priority message is send the first

-

If a message is corrupted, it is resent automatically

-

If more than 8 bytes of data must be transmitted, data is divided in packets of 8 bytes and several messages are generated consecutively

5 Exposure control

Exposure control master is the CPU core:

Once the system connected to the generator is known, the CPU downloads the exposure control configuration stored in a FPGA (DSP also in the case of PPC control board).

Then, the CPU manages the slow functions while the FPGA manages the hard real-time functions:

FPGA:

-

Handles the system/generator IO lines (including exposure command lines, brightness...)

-

Triggers/cuts the exposure

-

Handles the HV power inverter safeties signals (by the DSP in case of PPC kv control board)

-

Handles Xray On signal

-

Generates the 1KHz microprocessor main interrupt

CPU

-

Update the exposure state machine based on the signals send by the FPGA

-

Generates the exposure enable to the FPGA once everything is ready for the exposure

-

Calculates and applies kV, mA, exposure time,

-

Counts the exposure time

-

Regulates mA each 1ms

-

Handles heater and rotation errors

-

Manages the event and error log

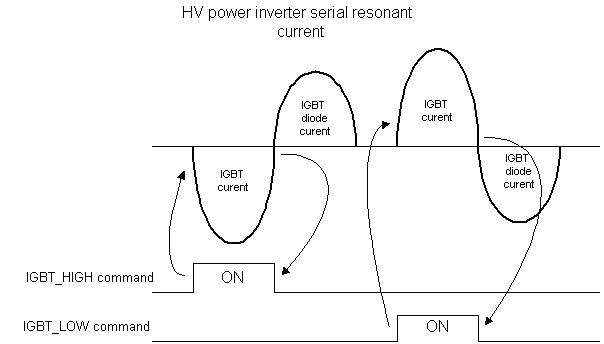

6 HV power inverter control

This function is controlled by the DSP and FPGA.

It handles the HV power inverter state machine. This state machine goes into its active states when exposure control function triggers the exposure. Then the state machine successively drives each IGBT gate.

The delay applied between two consecutive IGBT “on” commands is calculated inside the DSP in the case of the PPC board.

This is the minimum time of the following two:

-

The parallel resonance time which represents the max delay not to go over ( the inverter must not be driven below the parallel resonance frequency )

-

The time calculated by the kV regulation

This second time is the result of the kV regulation loop whose role is to make the measured kV equal to the kV demand:

-

kV measure is subtracted to kV demand to create error_kV (digital for the PPC board)

-

error_kV is divided in two parallel chains made of a kV error peak detection followed by a analog to digital conversion ( analog )

-

The digital error then feeds a digital PI (proportional Integral) regulator, which calculates the delay to apply before triggering the next IGBT, computed by the DSP in case of PPC board.

Each IGBT “off” command is triggered by the 0 Amps crossing of the serial resonant current.

Figure 2. HV power inverter serial resonant current

In case of tube spit, the state machine goes to the “off” state, stays 100us inside it and automatically restart if the maximum number of tube spits is not reached.

At the same time, the main software counts the number of spits and informs the system with a process depending upon the application.

IGBT commands from the FPGA then goes through drivers to the inverter. The drivers can be disabled by a mains drop or an incorrect gate supply.

The IGBTs gate drive supply is controlled synchronously with the inverter state machine:

-

gate supply voltage is read and compared to a reference

-

each two IGBT command, the gate supply IGBT is commanded with a duration proportional to the gate voltage error

-

between two exposures, the inverter being not running, the gate supply is regulated by at a fixed (8KHz) frequency. Constant gate supply voltage is ensured by regulating the gate supply command pulse width.

7 HV chain measure and safeties

HV chain is protected by fast and slow safeties.

Fast safeties are implemented in analog form and cut the HV power inverter state machine in case of error:

-

over kV

-

no kV

-

kV regulation error

-

Anode spit (after the max number of tube spits allowed for the application/tube)

-

Cathode spit (after the max number of tube spits allowed for the application/tube)

-

Max resonant current

-

Gate supply ok

Slow safeties are based on measures made by the micro controller:

The following signals are measured each 1ms:

-

kV measure

-

kV unbalance

-

kV demand

-

mA measure

-

HV tank temperature

-

gate supply voltage

-

DC Bus voltage

These measurements provide a second way to detect a fault condition in the HV chain and put the generator in a safe state.