- Topic ID: id_16158103

- Version: 3.0

- Date: Apr 9, 2020 8:44:49 PM

Collimator Theory of Operation

The mechanics of the collimator are controlled by firmware. The Collimator Control Board (CCB) is the interface between the firmware and the mechanics. The basic function of the collimator is to set the x-ray beam width at the patient and provide filtering of the beam for the proper “hardness”.

This module is split into the following sections:

1 Collimator Control Board (CCB)

This Collimator Control Board has five major functions:

-

The Core Controller for processing and control.

-

Communications using the Controller Area Network (CAN) Interface with Fault & Reset signals.

-

CAM positioning.

-

Filter positioning.

-

Voltage regulation and referencing.

1.1 Major Function List

Table 1 lists the major functions of the CCB.

1.2 Location of Parts

Figure 1 shows the location of parts on the CCB.

Figure 1. Location of Parts (CCB)

2 Core Controller

The “Core controller” shares functionality with the controller section of the Data Acquisition Control Board (DCB). The core section consists of the processor, clock and clock processing, RS232 circuitry, Flash memory and RAM.

2.1 CPU332

This comes with a 16 MHz clock and the Standard TPU (Time Processor Unit) with enhanced PPWA (Period/Pulse-Width Accumulator). The TPU is essentially a dedicated processor for time related functions.

2.2 Clock and Clock Loss Circuitry

The processor clock is derived off a 32.000MHz crystal oscillator, which is divided down to 16 Hz, which is fed into the processor. The clock runs through the processor and exits the chip at the CLKOUT pin before feeding the rest of the board. If the clock stops for over 9.9 mS, the missing pulse detector will pull the reset bus line low and set the clock loss bit in the Altera. This bit can only be reset by firmware command (or power cycling).

2.3 Reset Bus

There is one central Reset line on the CCB. This central line connects the CPU, the pushbutton reset, the external GCAN reset, the Background Debugging Mode connection, the Altera, and the 82527 CAN controller.

The external GCAN reset is applied by commanding GCAN_RST_P high relative to GCAN_RST_N. This puts the board into reset.

2.4 CPU Signal Buffering/ Conditioning

The CPU does not interface directly to any external devices. It buffers the signals through HCT244 devices. The following are inputs from external devices:

The CAM and Filter encoder signals are buffered inputs to the TPU as are the filter home switch and the DAS trigger signal. The Filter C pulse and the filter home switch are combined to form the filter home signal. The TPU is set up to decode the quadrature of the encoders and provides a 16 bit counter for each axis position.

The filter home switch contacts and the filter encoder C pulse are also buffered to the DATA bus through the “INREG” register (U24). That is the only register outside of the Altera used for data.

Outputs from the TPU are for the CAM and filter drives and these are buffered out through an HCT244.

2.5 TPU and CAM Drives

The TPU has a stepper motor control algorithm that is used for the CAM drives. The firmware sets of the TPU with the acceleration and deceleration rates and the step rate. When it sets the desired position the TPU takes care of the actual move. It is set up now for half step commands to the Vexta 5 phase stepper driver at a rate of 2000 steps per second for a standard aperture move.

2.6 RS232

The RS232 link is on the board purely for development reasons.

2.7 Power-Up Configuration

The Data3, Data9 are held low on reset to configure the 68332. Data3 low on reset release configures the /CS6 pin to be ADDR19 so we can access 1 MB of memory. Data9 low on release of reset turns the IRQ[7:1] lines into PortF outputs. Holding MODCLK low configures the 68332 to use an external clock source.

2.8 FLASH and RAM

The memory for the CCB consists of 8 Mbit (1 Mbyte) of 120 nS FLASH and the same amount of 55 nS RAM. The FLASH interfaces directly to the 68332. The RAM does not. The DCB uses the the same boot firmware. ADDR0 is not used on the memory. The read/write decode from the Altera handles the byte selection.

3 Gantry Controller Area Network (CAN)

3.1 CAN Function

The CAN controller chip is an Intel 82527. Firmware writes and reads from this chip to send and receive messages via the CAN. When pin 2 of the HCPL7101 is high, the output (pin 6) is high. The outputs (pins 6 and 7) of the 82C250 will be floating. This is the “recessive” bus state on the network. A logic zero from the 82527 will result in GCH (Gantry Can High) being pulled to high and GCL (Gantry Can Low) being pulled low.

3.2 LED Function

The 82527 has two ports on it: one is used as the data bus interface to the rest of the board; the other is used to light LEDs. The function of these LEDs are defined by firmware.

3.3 Exposure Command

3.4 Trigger Clock

3.5 System Fault

3.6 GCAN Reset

3.7 CAM Drive

The CAM drive function consists of the clockwise and counterclockwise pulse commands to the stepper motor driver, encoder feedback, the driver disable signal and the driver current cutback inhibit signal. The clockwise and counter-clockwise pulses are derived in the Altera from quadrature pulses created by the TPU in the 68332. The rate of these is under firmware control. The TPU also decodes the encoder signals to keep track of the count and direction of movement.

Two control signals from the 68332 are for controlling the behavior of the Vexta, 5 phase stepping motor driver. Essentially the 68332 writes to a register to set the signals CURR_HOLD and CAM_OFF_OUT.

When CURR_HOLD is high, it turns on FET Q35 and prevents the stepping motor driver from automatically decreasing its drive to the motor. Normally the current gets cut back by half after a move because it is not needed for acceleration and movement.

When the CAM_OFF_OUT signal goes high, it turns on a FET Q36, which turns off the stepping motor driver and allows the CAMS to “freewheel”.

3.8 Filter Drive

The filter driver is a basic H-bridge with high side current sensing for each phase. Sensing the high side allows protection for output shorts to ground. The stepping signals come from the TPU and decoded by the Altera to sequence the high and low FET drive signals.

3.9 Current Limit

The current limit circuitry is the same for both phases. An instrumentation amplifier with high common mode rejection senses the current through an effective 0.25 ohm resistance. The output of the amplifier is then fed into two comparators. One comparator is for pulse to pulse current limiting and the other is the short circuit latch comparator. For pulse to pulse current limit, the voltage regulators are divided down to create a reference voltage. This reference is fed into the comparator and when the output from the sensed current exceeds the reference, the comparator switches and shuts off a latch, which turns off the top FET. This cycles at a 15 kHz rate because of the clock into the latch.

3.10 Short Circuit Function

The short circuit protection circuitry uses the same concept as the pulse to pulse limit except on a short, the rate of rise of the current is so fast that the current sensed can rise to just over 10 A. This is limited by the 6.8 uH inductor on the board and the reverse recovery charge of the lower FET's parasitic diode. As the current passes the short circuit reference voltage, a comparator switches in a latch that cuts off drive to the top FETs. Only firmware can reset this latch so current stays off after a short until firmware commands otherwise.

3.11 Current Cut Back

The Current Cut back function drops the current to the filter. This keeps the motor from unnecessarily dissipating power when it is not moving. The firmware can command this, which then turns on Q5. When Q5 is on, it drops the pulse to pulse current reference.

3.12 Basic H-Bridge Function

The H-bridge uses two high side gate driver chips per phase. These create floating voltages to drive the top FETs without transformers or optical circuitry. The resistor - diode combinations around the inverters which feed the gate driver chips and the gates of the FETs are set up to prevent "shoot through" or simultaneous conduction. This is prevented by turning on the FETs slow and turning them off fast. The SD signal into the ir2110 devices disables drive until a command occurs. Holding SD high disables the driver.

3.13 Filter Home Switch

The filter home switch tells the CCB when the filter is physically positioned “at home” of course. It does this by feeding back the normally open and normally closed contact signals, which can be read at register U24 (Address 0x800000/1 in the memory map). When at home, the normally open switch is closed and the normally closed switch is closed.

3.14 Voltage Regulators and Reference Voltages

The voltage regulators create voltages for the FET gate drivers (12V), and the instrumentation amp (± 8V). The 8V signal is for the pulse to pulse and short circuit currents.

3.15 Altera Functionality

The Altera functionality is covered in the Programmable Device Logic (PDL) specification 2208487PDL.

3.16 I/O Bit Map

With the exception of the INREG register (Address 0x800000), the input and output registers are in the Altera.

3.16.1 Output Register

3.16.2 Z-Axis Tracking Timer

Within the Altera chip there is a timer-counter function. One function provides 125 kHz for the quadrature decode functions and 15.6 kHz to the filter amplifier circuitry on the CCB. Both these clocks are derived from the 16 MHz crystal derived clock.

For the Z-Axis function there is a 14 bit “up” counter with a clock of 3906 Hz derived from the 16 MHz system clock. The timer function comes from the ability to load a digital comparator that compare the value loaded by firmware against the value of the counter. Firmware is given the capability of asynchronously loading the counter, clearing the counter and masking the interrupt that is generated when the compare and count value match.

There are 3 control signals that configure this function:

The interrupt is generated when the count matches the compare value.

3.16.3 Collimator Register

The collimator register is used for collimator specific functions. It allows the firmware to command and readback status on the filter drive amplifier currents and also allows the firmware to shut down the collimator cam drives.

3.17 Z-Axis Tracking Overview

-

The purpose of tracking is to follow the focal spot so that the system can keep the umbra of the beam on the detector to reduce dose and still avoid artifacts.

-

Dose reduction is approx. 40% less in the 4 x 1.25mm mode and 25% less in the 4 x 5.00 mode.

-

Z-Axis tracking is needed because the focal spot moves in Z due to thermal changes in the tube, and in mechanical forces during Gantry rotation and tilt.

-

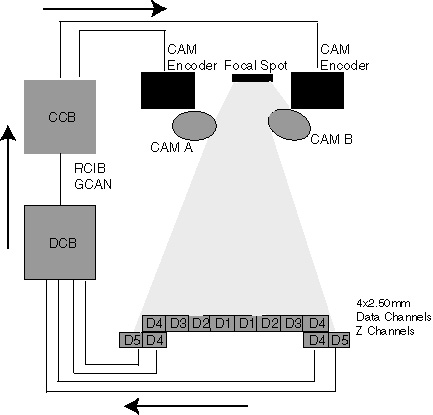

Z-Axis tracking involves the X-Ray Tube Focal Spot, Collimator, Detector, DAS, DCB, CCB, and RCIB/GCAN Communication Networks.

Figure 2. Typical Tracking Feedback Loop

3.18 Collimator Tracking Control Loop Theory

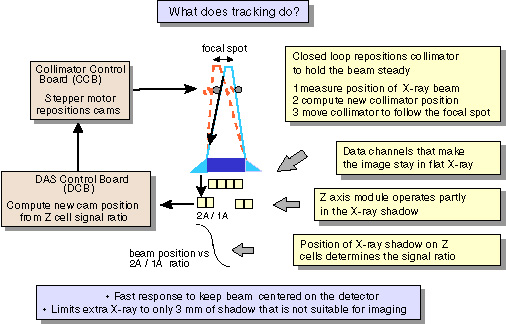

The purpose of tracking is to follow the focal spot so that we can keep the uniform X-ray of the narrowest possible beam on the detector to reduce dose and still avoid artifacts. The focal spot moves in Z due to thermal changes in the tube and a mechanical forces during gantry rotation and tilt angle. Each cam is basically an independent system.

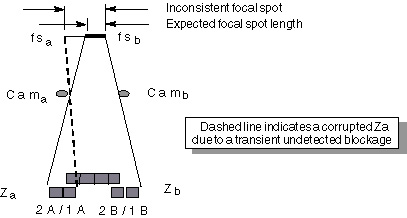

Figure 3. Tracking Diagram

-

Select a safe operating point at the edges of the detector (target beam position at isocenter).

-

Sample X-ray beam position every view and adjust collimator CAM positions every 20 ms. to keep the beam at the ISO center channel operating point.

-

Compute Z ratio for each side of the Z module (outer row)/ (inner row). (Channels 763, 764, 765, 766, 767 & 768.)

-

Convert the ratio to a beam position at the Z module.

-

Compute the focal spot position given the beam position on the Z module, the cam position for the Z module, and geometric magnification factors at the Z module.

-

Compute the new cam position for the isocenter channel given the focal spot position and geometric magnification factors for the isocenter channel. During views when portions of the patient, patient table, IV line etc. block the Z module, the beam position measurement can not be used.

-

We will compare DAS data channel 762 (data channel adjacent to the Z module) to an expected signal as a function of the measured mA, DAS gain, and trigger period. The Z module is blocked if either inner row is less than 0.9 times the expected value. During a blocked condition, the cams will hold constant at the last unblocked position.

note: Transient conditions during a tube spit do not require special action. -

Measure the beam position and readjust the collimator approximately every 20 ms.

-

-

Scan aborts will occur when the following conditions exist.

-

Beam position on detector, non-blocked z-chnls condition, is out of tolerance by +/- 0.4 mm of desired position for more than 100 mSec.

-

Signal Corruption of chnls 762 through 768, where zero or negative values (counts) are detected for more than 200 mSec OR generator mA feedback to DCB is less than 4 mA for more than 200 mSec.

-

Focal spot length error for more than 4000 mSec

-

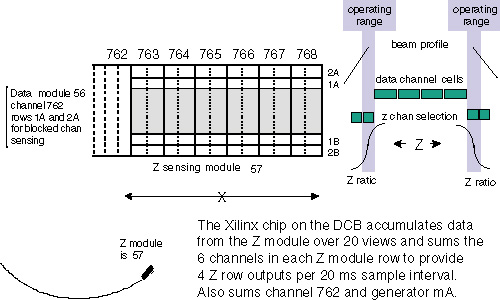

Figure 4. Z Sensing Module

3.19 Tracking Loop Variables

3.19.1 Blocked Channel Check: 762

The x-ray signal output of DAS Channel 762 is characterized during FASTCAL (Air Scan with No beam obstructions). During patient scanning, if the x-ray signal on DAS channel 762 falls below 10% of the signal characterized during FASTCAL, then it is considered “blocked” and the collimator CAMS will hold constant at the last “unblocked” position.

3.19.2 Z-Channels

-

The Z-Channels are DAS channels 763, 764, 765, 766, 767 & 768.

-

Each DAS Z-channel is a combination of 2 detector channels in the X direction.

-

Z-Channels have a different Detector Row selection than Data channels. This is selected by the Z-FET control lines.

-

Beam position is determined by the following equation:

Figure 5. Equation for Beam Positioning

The R value is then transformed into a 4th degree polynomial to find the Z-Axis Beam position, which determines beam width at detector (mmd) and focal spot length (mmf).

mmd = millimeters at detector

mmf = focal spot length in millimeters.

OVERRIDES: value = {

RX_OVERRIDES: value = 0xa

FILAMENT_I: value = 0.0000

ANODE_DAC: value = 0x0

CATHODE_DAC: value = 0x0

ROTORSPEED: value = ROTOR_SPEED_HIGH

XRAY_DELAY_SEC: value = 0.0000

XRAY_DURATION_SEC: value = 1.0000

DCB_OVERRIDES: value = 0x20

Puts the DCB into over-ride mode so FET control can be selected.

CANNEDDCBPATTERNSELECTION: value = 0x0

CANNEDCNVPATTERNSELECTION: value = 0x0

AUTOCORRECTIONDISABLEMASK: value = 0x0

INNERCHANNELCONTROL: value = 0x3

Controls the Center DAS Chassis FET configuration

OUTERCHANNELCONTROL: value = 0x3

Controls the Right and Left DAS Chassis' FET configuration

ZCHANNELCONTROL: value = 0x9

Controls the Z-Channel FET configuration (Channels 763, 764, 765, 766, 767 & 768)

INJECTEDDCVOLTAGE: value = 0x0

CCB_OVERRIDES: value = 0x2

Puts the collimator Control Board in over-ride mode

COLLIMATORWIDTH: value = 0x22c4

Keeps the collimator Cams wide open to flood the Detector

3.19.3 Focal Spot Length Check

During some conditions the Z module measurement can be corrupted due to a transient undetected blockage or due to a tracking loop malfunction. These conditions can be detected, identified by the DCB firmware, and reported to the gesyslog.

The focal spot length is computed on each sample interval from the measured Z and Cam positions.

-

If Z measurements from each side are both valid, then the computed focal spot length should be close to the expected focal spot length from FastCal.

-

If the computed focal spot length is not within tolerance of the focal spot length determined during Fast Cal then the control loop will hold the current cam positions.

-

If the inconsistent length condition continues for more than 400 msec without a normal blocked channel indication from channel 762, then the loop is assumed to be malfunctioning and the scan is aborted.

Figure 6. Focal Spot Length Check

3.20 Special Tracking Characterizations

3.20.1 Mylar Window Check

-

Takes 4 scans (1 scan at each Patient Acquisition Mode). If a 20 view average of channel 762 falls below .95 of the expected value, then an error prompt informs the user to check and clean the Mylar window.

-

Scans are taken without tracking and the collimator fully open to flood all detector rows.

-

Technique is 80KV / 20mA / 1 Sec. / Air Filter

-

Mylar window check is completed before DAS Gain Cal, Collimator Cal, and FASTCAL.

For more information, see “Dirty Mylar Window Scan,” in FastCal procedure.

-

Characterizes the differences in DAS Gain (gain ranges 1-31) for DAS channels 762 (used for blocked channel detection) and Z-Channels (763, 764, 765, 766, 767 & 768).

-

The differences are a result of Pre-Amp Gain Capacitor tolerances on converter boards 47 and 48.

-

The serial numbers of converter boards 47 and 48 are queried and stored during DAS Gain Cal. Collimator Cal and FASTCAL query the DAS and compare the serial numbers since the last time DAS Gain Cal was completed.

-

A DAS Gain Cal is required whenever DAS Converter boards 47 or 48 are swapped or changed.

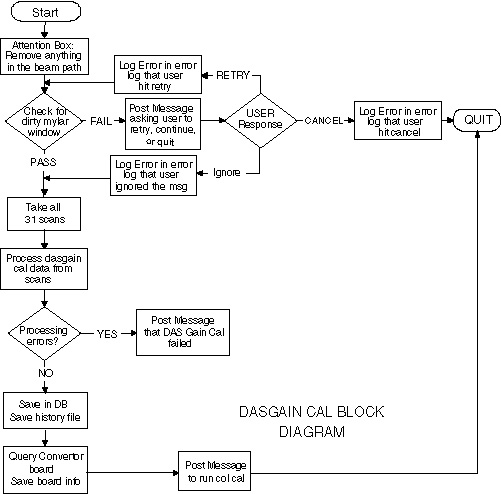

DESCRIPTION

DAS Gain calibration is required to support Z axis tracking. The ratio formed by the Z modules that is used as the basis for beam positioning is effected by the DAS gain selection. Capacitor tolerances on the DAS converter cards can change the ratio causing a beam position error. To avoid this error we measure the outer to inner row gain variation to develop a Z ratio correction factor for each gain selection.

DAS Gain Cal also determines a gain independent blocked channel threshold for the inner rows of DAS channel 762 for the tracking firmware. This gain factor is used to scale the gain normalized blocked channel scale factor to the proper level in the tracking firmware.

The DAS Gain cal flowchart is shown below. Before DAS Gain scans are taken, a mylar window check is done to ensure that the window is clean. Otherwise it can corrupt the tracking cals.

If the check succeeds, the DAS gain scans are taken and the cal proceeds forward. If the check fails, a pop-up is posted asking the user to provide inputs on whether they want to quit, continue anyway or retry the mylar window check after cleaning the mylar window.

Figure 7. DAS Gain Cal Block Diagram

DAS GAIN CAL SCANS

-

DAS Gain Calibration consists of 31 scans that are taken consecutively.

Stationary / 120KV / 20mA / 0.3 Sec / Air / Gain 1

through

Stationary / 120KV / 20mA / 0.3 Sec / Air / Gain 31

-

Processing is completed after all scans are completed.

-

Total time is approximately 4 minutes.

-

DAS Gain Cal takes 31 scans to collect signal data for all DAS channels at each of the 31 DAS gain settings using the DAS Gain protocol file.

3.20.2 Collimator Cal

Characterizes the beam position based on x-ray signal vs. collimator encoder position.

Eighteen Air scans are taken: one for each available application data collection mode.

-

All scans with z-tracking off

-

Scan time is 5.9 seconds

-

Thin Twin is 6.5 seconds

-

Stationary Scans

-

Offset from Nominal: ±900 cts.

-

#of views: 100 at each step

-

Step size: 50 cts.

-

# of steps: 37

FASTCAL completes 1 Collimator Cal (Sweep) Scan each time FASTCAL is run.

3.21 Diagnostics Related to Z-Axis Tracking

-

Diagnostic Data Collection Tool.

-

FET Override mode

-

Create and apply non-tracking Cal and DDC Scan

-

Z-AXIS ERROR CODES

Many of these messages contain variable fields for which some text or values will be substituted.