- Topic ID: id_16158020

- Version: 1.0

- Date: Jul 7, 2018 4:32:26 PM

Pancake DAS 16 Theory

1 Overview

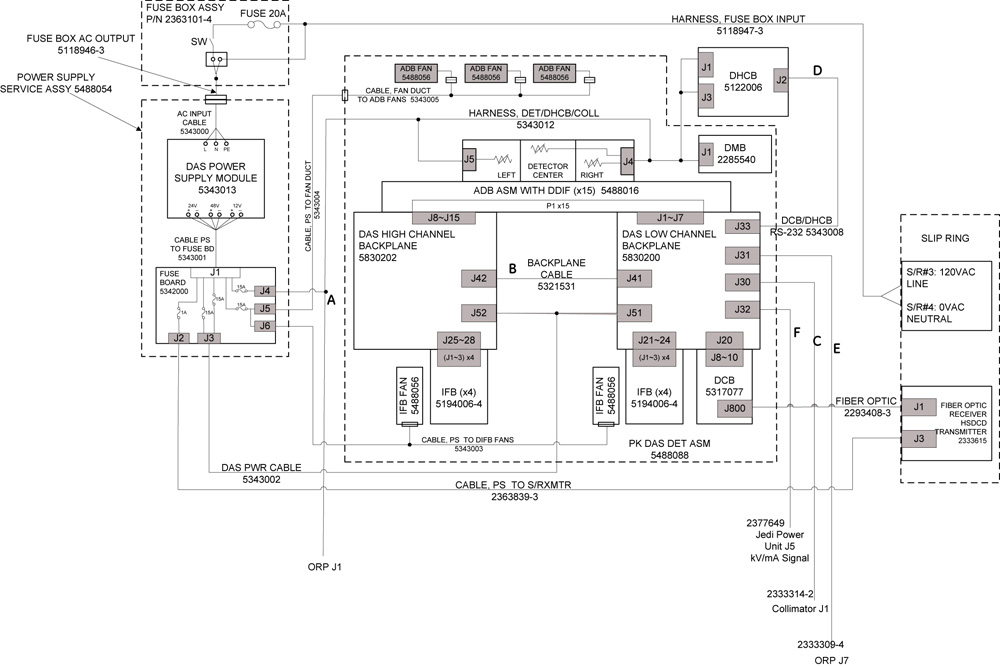

The purpose of Pancake DAS is to accumulate snapshots (called views) of the X-ray image of the target, and move those snapshots through a high-speed link to the Host for processing. Each view is started by a trigger, which can be generated externally or internally (by a timer on the DCB).

The purpose of the DCB firmware is to set up and control the hardware needed to acquire views and transmit them to the Host.

The hardware consists of the FPGA components on the DCB, the IFBs and their associated ADBs (A/D converter board). The DCB sends requests to the IFBs/ADB to control them, or to query them for their status and/or settings.

It should be noted that the view data is not directly managed by the DCB firmware. The DCB FPGA is responsible for view acquisition from the IFBs/ADB, and transmission to the host. The DCB’s firmware provides control information for the DCB FPGA to properly manage the data flow through the DAS and onto the Host.

The DCB itself is controlled via requests from the Host. Among the most important of the requests is the scan Rx, which, as the name implies, is the prescription for the scan. It provides the parameters needed to control the scan, including such information as the trigger frequency, the number of views to acquire, the starting view angle, and so on. Beyond the scan Rx, many other communications also come from the host, including status queries.

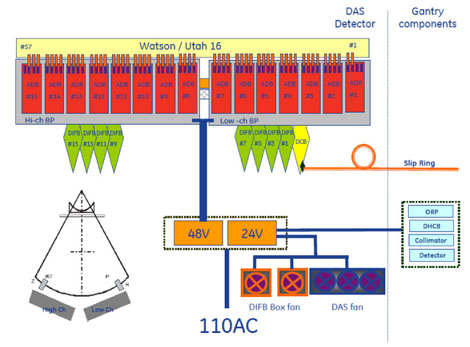

Pancake DAS and Detector is comprised of the following components:

-

X-ray detector and DAS interface (X-Ray detector and DAS Interface)

The primary function of the Detector is to convert X-ray photons into electrical current, which is sent to the Data Acquisition System (DAS) for signal amplification and analog to digital conversion, before being sent to the Recon Unit for image reconstruction.

-

A/D converter board (ADB board) (A/D Converter Board (ADB Board))

The ADB board process the low current signals from 4 detector modules outputs (including A and B side of each module) and converts these signals into digital signals. There are 15 ADB boards located on two separate backplane boards, low channel backplane and high channel backplane.

-

Digital Interface Boards (DIFB) (Digital InterFace Boards (DIFB))

The DIFB's are the Digital interface boards that take the ADB board digital output signals and send them to the DCB. There are 8 DIFB's for the Pancake DAS 16.

-

DAS Control Board (DCB) (DAS Control Board (DCB))

The DCB is the main control board for the DAS. It packages all the interface card data into a single high-speed serial data stream.

-

Backplane (Backplane)

The DAS Backplane is comprised of 2 boards that contain passive components only. The backplanes route a calibration reference level signal from the DCB and power supply voltages to the FRDM's as well as transmitting digital signals.

-

Air Plenum (DAS Air Plenum)

The Air plenum is comprised of 3 fans and filter assembly. Air plenum assembly provides proper heat dissipation for DAS components. The DAS heat dissipation is separate from the detector heat control. The detector temperature is controlled by DHCB board. Refer to Detector Heater Control Board (DHCB) theory for details.

-

48V Power supply (Power Supply)

The 48V power supply is a single power supply on the rotating assembly that powers most all of the components. This supply is not specific to the DAS. All voltages used by the DAS and Detector are generated via on board regulators on the DCB and DIFB's.

-

The Detector Heater Control (DHCB) board theory can be found in the Gantry Thermal Theory document.

Figure 1. PDAS Block Diagram

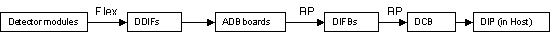

Figure 2. Data flow in PDAS

2 X-Ray detector and DAS Interface

2.1 X-Ray detector output signals

The smallest element of the X-ray detector matrix is a detector pixel. The detector pixel has a current output that is proportional to the incident X-ray flux.

Some applications will include the connection of multiple pixels in parallel to a single DAS preamplifier channel. The connection means is a FET switch array, that is external to the DAS and converter card and is in the detector assembly or module. The FET array will connect pixels in the ”Z” direction, which is the direction normally parallel to the longitudinal axis of the patient. Up to eight pixels may be connected in this manner. The output of such interconnected pixels shall hereafter be referred to as a detector cell. If an application includes pixels, which are not connected to an output cell or preamplifier input, such pixels will be connected to electrical ground by the FET array, or in part of the DAS external to the Converter Board. The disconnected pixels will present a FET off impedance to the DAS.

For most DAS channels, the detector cell aperture is one cell column or 1mm long in the azimuthal direction. However, some cell outputs will be digitally combined by DCB in either pairs or triplets in the azimuthal direction to form 2mm and 3mm cells. Detector cell so connected will be termed “ganged” cells.

2.2 Detector and DAS interface

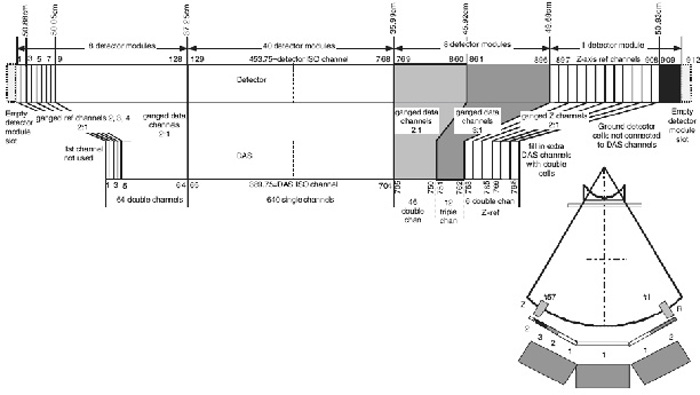

The Watson 16 detector has total 57 detector modules, 912 detector channels which are used to connected with Pancake DAS. Pancake DAS data channel number is 768ch, which is the same as GDAS16. This is achieved through digital ganging the 912 detector channels to 768 DAS channels (The ganging is done after A/D conversion).

The ganging format is shown in below diagram:

Figure 3. Detector_DAS_Ganging

Detector channel 1-128 corresponding to DAS channel 1-64 with ganging ration 2:1.

Dtector channel 129-768 corresponding to DAS channel 65-704 without ganging.

Detector channel 769-860 corresponding to DAS channel 705-750 with ganging ration 2:1.

Detector channel 861-896 corresponding to DAS channel 751-762 with ganging ration 3:1.

Detector channel 897-908 corresponding to DAS channel 763-768 with ganging ration 2:1.

Detector channel 909-912 are grounding.

2.3 Detector and DAS connection

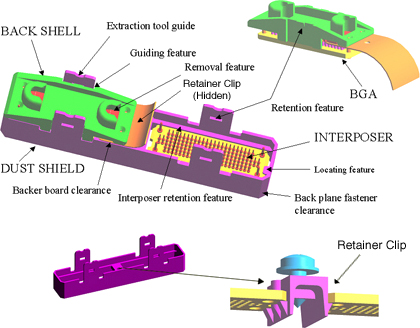

Watson 16 detector and Pancake DAS use the same DDIF connectors as GDAS to transfer signal and power, which is shown in Figure 4

Figure 4. DDIF Assembly

3 A/D Converter Board (ADB Board)

3.1 Overview

The ADB assembly is designed for Pancake DAS 16 slice system. The main functions of the ADB are:

-

Provide DDIF (DAS Detector Interface) connection, which is same as current 16-slice system. Each ADB holds 4A/4B detector modules (each detector module has 16 detector channels).

-

Employ 16pcs GDAS ASIC rev 4 (CSP package) processing analog low current from detector cells outputs and converts them into digital.

-

FET lines will be provided by DCB. To design common ADB, two groups of FET lines goes through ADB to Watson detector. If the ADB is on the low channel side of the DAS, then FET lines include Low-Z, reference control. If the ADB is on the high side of the DAS, then FET lines include High-Z, besides active data modules.

-

Receive configuration instructions and scan commands data synchronized with clock from DIFB board. ADB converted DAS data will be shifted out and transmitted to the DIFB.

-

The two output serial data streams to the DIFB are same as data format of VCT HALO ADM. One is even group of 8pcs ASIC and the other is odd group of 8pcs ASIC channels arranged respectively. Each DIFB can receive DAS data from 4 serial data streams from 2 ADB board, total 32pcs ASIC data.

-

The two output serial data streams to the DIFB are same as data format of VCT HALO ADM. One is even group of 8pcs ASIC and the other is odd group of 8pcs ASIC channels arranged respectively. Each DIFB can receive DAS data from 4 serial data streams from 2 ADB board, total 32pcs ASIC data.

-

ADB will do thermal tracking and alfa-calibration controlled by DIFB. Internal and external reference current will be used.

-

In order to get better thermal performance, heat sink over 16 ASICs should be conduct heat correctly by package thermal design.

-

Provide diagnostic LED for debugging the status of the board.

-

The ADB are designed common that they are interchangeable between each other.

3.2 Temperature Monitor

The ADB have two on board temperature sensors that monitor the board temperature to ensure that the PDAS ADB are operating in its proper temperature range. The temperature sensor temperature will be read via the I2C interface. Temperature will be sampled during each view and send to DCB.

3.3 Power Requirement

The ADB are designed to use the following power supply voltages. Total maximum power requirement should be under 25.6W.

3.4 Power on and Warm up

The -2.5V analog should be up before +2.5V analog, +2.5V digital. This will be controlled by DIFB output. The maximum required elapsed time from power-on to full to specify ADB performance should be less than one hour. Time to meet full specified ADB performance shall be computed on the basis of two minutes warm-up per minute since power was last on or one hour, whichever is less. However, under no conditions where the power has been temporarily turned off, shall the required warm-up to meet full performance specification be less than 20 seconds.

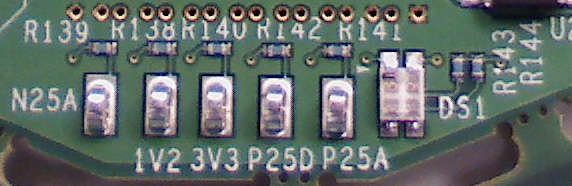

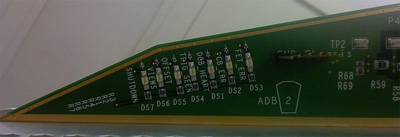

3.5 Test points and LEDs on ADB board

Figure 5. ADB LED's and Test Points Layout

Figure 6. ADB Block Diagram

The ADB provides some test points on Power and Ground.

A dual color (orange + green) LED provided on ADB to indicate the following information.

4 Digital InterFace Boards (DIFB)

4.1 General

The DAS interface board that is abbreviated as DIFB, which acts as an interface bridge between the ADB board and the DAS control board (DCB). The DIFB processes multiple low speed data streams from the ADB boards and then sends high-speed data to the DCB in a serial stream.

4.2 Processing

The DIFB performs the following functions:

-

Voltage Regulation

-

Power Supply Sensing

-

Voltage Monitoring

-

CAN Interface to DCB

-

Data Formatting (FFP)

-

Serial Interface with the ADB boards.

-

ASIC Control

-

Point-To-Point Data Transmission to DCB

-

Offset Compensation

-

Linearization

-

Temperature Sensing

-

Diagnostics

4.3 Interface Overview

The 16-slice Pancake DAS system architecture has 8 DIFBs each of which communicates with two ADBs. The only exception is the first DIFB (#1), which is only connected to ADB #1. The DIFBs are numbered by odd numbers only (1,3,5,7,9,11,13,15) since they are in the odd numbered slots of the DIFB chassis and need to line up to the backplane connector.

4.4 ADB Interface

-

One DIFB communicates with two ADBs. The DIFB has separate transmitting and receiving lines for each ADB. The data lines are Low Voltage Differential Signals (LVDS).

-

It is a source synchronous design. Both transmitting and receiving data are transmitted with their clocks. The clocks are LVDS signals.

-

There is a separate reset signal from the DIFB to the ADB boards. The reset signal will reset the DAS ASICs and FPGA. The reset signal is derived from the DCB reset signal.

-

The DIFB supplies power to the ADB boards.

-

A signal is also used to specify if the ADB boards are present or not. The signal is an active low signal.

-

Only odd numbered DIFB's can configure the A/D board FPGA. This was necessary to be completely compatible with the VDAS32 architecture and HDAS64 architecture, both of which only have odd numbered DIFB boards.

4.5 Serial Data Format

Channel data read is a kind of the sequential read operation. The DIFB reads 4 serial data buses at the same time with a burst mode.

4.6 DCB Interface

The interface between the DIFB and DCB is a point-to-point connection. A serial data output signal is a pair of low voltage differential signals. The trigger signal from the DCB initiates a view collection. During the initialization, the DIFB sends a series of the training patterns to the DCB. Once the DIFB is ready to send channel data to the DCB, the DIFB sends a 16-bit word header, the 1040 (32-slice) or 2080 (64-slice) data channels, and 16 auxiliary data for temperature signals and diagnostic data. Between the each view, the training pattern will be transmitted.

4.7 CAN Bus Serial Interface

The CAN bus is used to communicate with the DCB and other IFBs through a CAN transceiver. There are only two serial lines to be connected on CAN bus: CAN_Hi and CAN_Lo (Differential , bi-directional signal pair). Communication is accomplished through a command/acknowledge protocol.

Each DIFB connected to the bus is software addressable by an unique address and each DIFB shall have its own unique address, known as its slave address. This address is determined by the DIFB backplane connection and the unique address is determined by the DIFB's location in the backplane.

4.8 I2C interface

The DIFB and ADBs have separate I2C data lines. A multiplex in the FPGA will select which I2C bus will be used.

Besides one I2C temperature sensor for itself, the DIFB also writes to and reads from two temperature sensors and one serial EEPROM for each ADB it is connected to. All sensors and EEPROMs are tied through a 2-wire serial interface (I2C bus).

4.9 LED's

The following test points and LED's are available on the DIFB. There are no adjustable power supplies in the DAS subsystem.

Figure 7. DIFB Board Layout

5 DAS Control Board (DCB)

The DCB is the main control board for the Data Acquisition System (DAS). It packages all the interface card data into a single high-speed serial data stream, compatible with the receive function on the DAS Interface Processor (DIP).

5.1 Inputs

From Interface Boards (DIFB):

-

Serial Data Streams

-

DIFB CAN Bus communication for status, faults, chassis temperature readings, and serial number information

-

Interface Board Fault Line

From On-Rotating Processor (ORP):

-

Input View Triggers

-

RCIB CAN Bus communication for scan prescription information and FLASH download

-

RCIB CAN Fault Signal

From Detector Heater Control board (DHCB):

- RS-232 Bus communication for status, faults, detector temperature readings, and detector identification information

From Generator:

- KV & MA analog signals

From Backplane:

- Power supply voltages

5.2 Outputs

To Interface Boards:

-

Shift Clock

-

Trigger Signal

-

Converter CAN Bus communication for control information

-

Reset signal

-

External reference current

To On-Rotating Processor (ORP):

-

RCIB CAN Bus communication for DAS status, error, or scan complete information

-

RCIB CAN Fault Signal

To Detector Heater Control board (DHCB):

- RS-232 Bus communication for control information

To Detector:

- FET Control signals

To Slip-ring:

- High-speed serial data stream containing the view data with embedded FEC CRC.

5.3 Processing

The DCB will perform the following functions:

-

Interfaces with the On-Rotating Processor (ORP) for Rx reception and scan completion via CAN bus.

-

Sets up gain and offset trim and controls the interface boards, via the DIFB CAN interface.

-

Receives triggers and starts acquisitions with the interface cards.

-

· Performs serial-to-parallel conversion on data streams from the interface boards, does parity checking on the data, and formats the data for view transmission.

-

Adds Forward Error Correction (FEC) to the channel data and sends it across the slip-ring to the Scan Reconstruction Unit (SRU) via the high-speed serial data interface.

-

Detects jitter and time-outs in the view trigger signal.

-

Controls the operation of the Detector Heater Control board and monitors the subsystem for faults.

-

Monitors the power supply voltages to make sure they are within the software programmable limits.

-

Acquires the kV and mA values for each scan.

-

Controls the FET switch array in the detector to change the number and thickness of scan slices.

-

Monitors the DAS subsystem for various faults.

-

Stores & sums the z-axis reference channels, and performs calculations that control the collimator cam positioning. This is used to track the x-ray beam and keep it centered on the detector.

5.4 Control Signals

Two broadcast signals from the DCB are used to control the sequencing of data onto the data streams.

The trigger signal will be used to initiate the sampling and transmission of all the channels on the DIFB.

In response to an external or internal view trigger, DCB will generate a trigger pulse to all of the interface boards through the chassis backplane. Both external and internal view triggers have the same effect on the DCB.

The only mechanism to reset the converter boards will be to assert the reset signal. This active high, single-ended signal is set by the DCB and sent to all interface boards through the chassis backplane.

An active low signal is generated by an interface board to notify the DCB in the event of a fault condition. Any one or more interface boards can assert this signal at anytime. When the signal is asserted, the DCB will interrogate all interface boards via the Interface Board CAN bus to determine the cause and report an error condition when appropriate. The actual interrogation is done by firmware.

The DCB produces an external reference current, to the interface boards for diagnostic purposes.

5.5 CAN Bus Signals In/Out

The CAN bus used between the DCB and the converter boards is a bi-directional serial communications bus which requires only two serial lines. Communication is accomplished through a command/acknowledge protocol, rather than a register-access protocol.

5.6 Data Signals In

The DCB will accept DAS channel data from the converter boards, per the following definition. The Interface Board processes digital channel data from the ASIC’s resident on the A/D boards. This data is combined with temperature measurements into a single point-to-point serial data stream to the DCB.

When the DIFB receives a trigger signal from the DCB, the DIFB starts to send its channel data. During the each view period, there will be some idle time, during which the DIFB will send alternating 1’s and 0’s (1 0 1 0 1 0 …) to maintain the lock.

5.7 Slipring Interface

The interface from the DCB to the console is designed to run at 2.488 Gbaud per link, where each link represents a physical channel on the slipring.

5.8 Host CAN Interface

The DCB Host Interface will be used to control DAS operation and to communicate DAS status. The following sections describe the control interface. The DCB Host Interface makes use of Controller Area Network (CAN) technology. The DCB’s use of this technology including the physical interface conforms to all CAN specifications. All CAN signals are optically isolated between the DCB and the network.

The DCB receives the external view trigger input from the ORP via a twisted pair wire. This input signal is optically isolated from the DAS and causes the DAS to begin view data collection.

5.9 Generator Interface

Measured scan kV and mA are read by the X-ray Generation Subsystem and fed back to the DAS so they can be inserted into the view data stream. The Generator Interface is implemented on a connector located on the backplane and signals are routed to the DCB via the backplane. These signals are differentially driven by X-ray Generation and received by the DCB.

5.10 Detector FET Control Interface

The DCB generates a maximum of 18 signals to configure the detector FET MUX circuitry. Each of the following 3 groups of detector modules uses a maximum of 6 of these signals for their MUX configurations: Z-axis Upper (ZUFET), Data Channel Detector (DFET), and Z-axis Lower (ZLFET).

5.11 Detector Heater Control board Interface

The DCB communicates with the Detector Heater Control board (DHCB) using an RS-232 serial communication interface. This interface provides the path for the DCB to setup and control DHCB operation, to monitor the DHCB subsystem for faults, and to obtain detector temperature readings for inclusion in the view data stream.

On power-up the DCB detects the presence of the DHCB in the system. If the presence of the DHCB is detected, the DCB will begin to communicate with the DHCB via the RS-232 interface through the CFC.

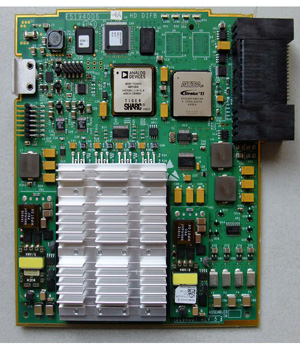

5.12 LED's

Below are the test points and LED's available on the DCB.

Below are the error code definitions (ERR_CODE LED):

Figure 8. DCB Board Layout

5.13 View Format

The DAS view data is shown as below:

Pancake DAS has the same view format as GDAS 16. But Pancake DAS has different view header from GDAS 16. Below table shows the differences:

6 Backplane

There are two backplanes for the Pancake DAS. One backplane is a “Low Channel” backplane that has one DCB slot, 4 DIFB slots, an inter-backplane connector, one power connector and sub-miniature D style connectors for DHCB, Generator Inputs and RCIB connections. This backplane interfaces to the lower numbered detector modules. The other backplane is a “High Channel” backplane and it consists of 4 DIFB slots, an inter-backplane connector and one power connector. The main power comes to each backplane separately and does not distribute between backplanes. The backplanes do not have any active components on them.

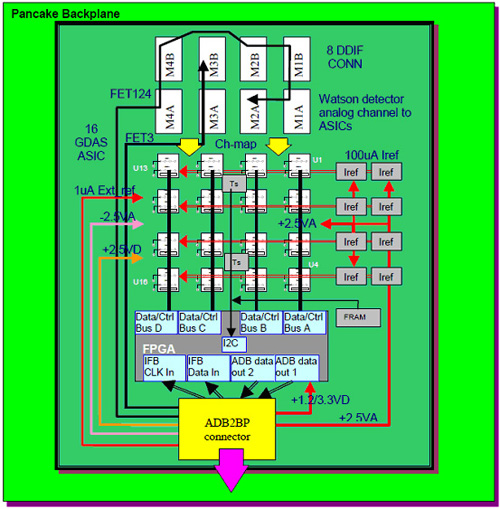

Refer to below Pancake DAS architecture diagram for the backplane connections with ADB boards, DIFB boards and DCB board.

Figure 9. PDAS BP Architecture Diagram

The backplanes for the Pancake DAS:

-

Convey the power to the X-Ray Detector, the DIFBs and the DCB.

-

Provide mechanical attachment and support for the DIFBs and DCB

-

Act as an interface between the ADB boards and the DIFBs to transfer the Digital data and control signals.

-

Provide for data and control transfer between the DCB and the DIFB cards.

-

Provide connectors for interfacing the DCB CAN bus communications to/from the Rotating Controller Interface Bus (CT-RCIB) and interfacing the DCB with the Detector Heater Control Board, and the generator kV and mA signals.

-

Provide diagnostic Error LED for displaying the state of the detector FET control.

-

Provide FET Command and bias lines. These are pass through signals from the DCB to the Detector module flex connections.

-

The DCB clock and trigger signals as well as the 48V power is routed on the backplane to groups of DIFB's.

-

There are 7 LEDs on Low channel backplane. These LEDs are from DCB board and show the status of DCB board. This make it possible to observe the DCB status without cover removal.

Below table shows the LED definitions:

Figure 10. PDAS BP LED's

7 DAS Air Plenum

7.1 Overview

The DAS air plenum is comprised of the plenum housing, filter assembly and 3 fans.

7.2 Fans

There are 3 fans mounted to a fan plate on the front of the Air plenum.

7.3 Filters

There is a single filter with honeycomb EMC shield integrated onto the back side of the filter. With the fan plate off the front of the air plenum, the filter side can be seen. The EMC shield is susceptible to damage so care must be taken when handling the filter assembly.

8 Power Supply

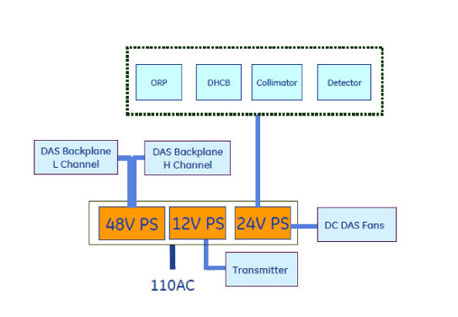

8.1 48V power supply

The 48V power supply is a single power supply on the rotating assembly that powers the DAS, Detector subsystem, Collimator, ORP, Detector heater control board and Slip ring Transmitter. All voltages used by the DAS and Detector are generated via on board regulators on the DCB and DIFB's. The ADB board power is supplied by regulators on the DIFB's. There are no voltage adjustments for the DAS components. The Power supply has an internal fan for cooling.

The architecture of Power supply is as below:

Figure 11. PDAS_Power_supply_architecture

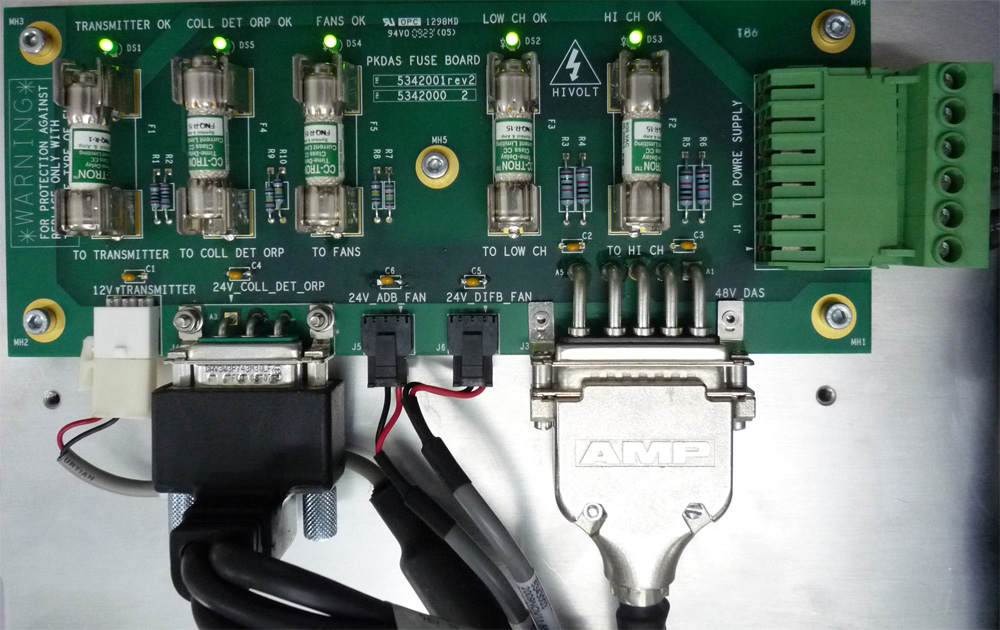

8.2 Fuse board

The Fuse Board provides a central point for fuse protection and distribution of 48Vdc power to the rotating harnesses and loads on the gantry. The board is powered by the main rotating 48Vdc power supply. The loads served by this board are: DAS, Collimator, DHCB, ORP & Slip-Ring Transmitter.

Figure 12. PDAS Power Supply Fuse Board LED's and Test Points